十天学会Matlab+FPGA的信号发生器设计

收藏

分享

脑图

十天学会Matlab+FPGA的信号发生器设计

课程介绍

本课程面向电子专业的学生和工程师,以硬禾实战营项目实战的训练方式,利用10期课程时间带领大家从项目分析到设计架构,从数字逻辑到FPGA开发,从Verilog HDL语言学习到功能模块设计,从UART串口协议到DDS原理解析,最终完成基于Matlab和FPGA-DDS可编程信号发生器设计。

通过课程训练,你将掌握FPGA设计流程、Verilog HDL编程应用、UART通信和DDS原理及FPGA模块的设计、IP核例化及Reveal在线分析的方法,对于提升硬件专业技能,备战电子设计竞赛,电子产品DIY,都是一次很好的训练。

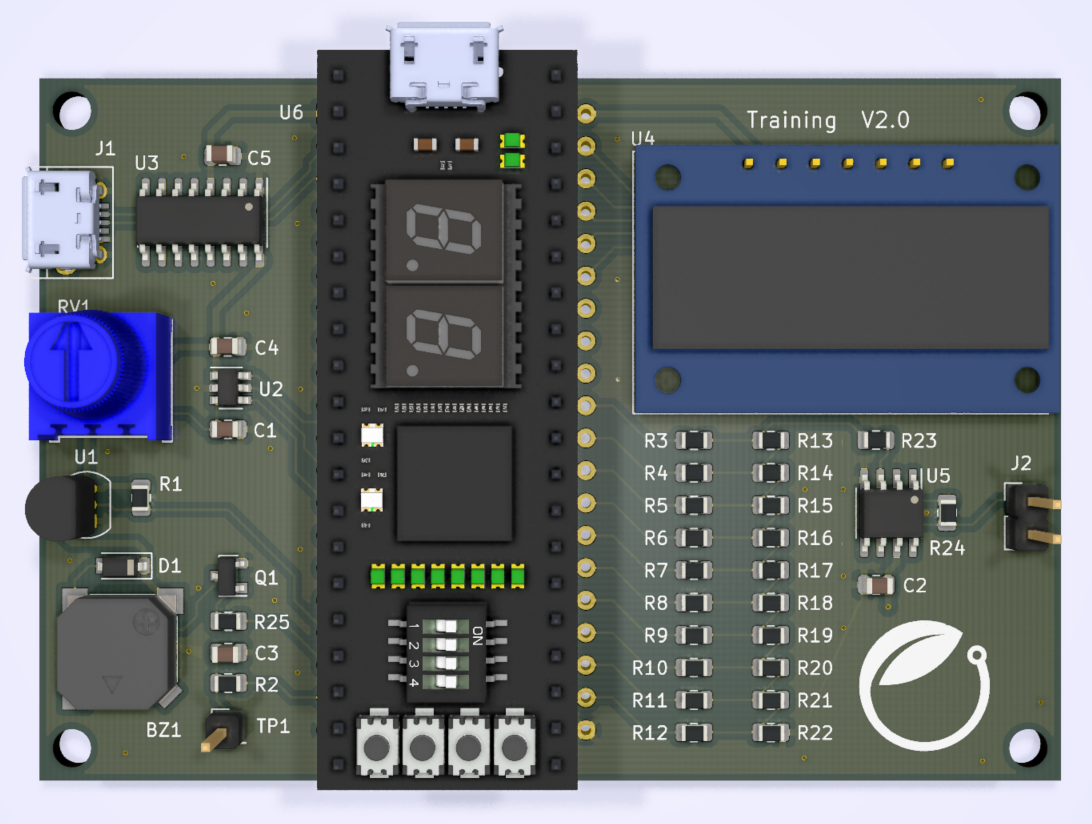

Training扩展板3D图

涉及技能

FPGA基础知识及开发设计流程

Verilog

HDL语言编程应用

IP核例化应用及Reveal在线分析

UART通信协议和DDS原理分析及FPGA驱动模块的设计

Matlab数据处理应用及与FPGA通信联调

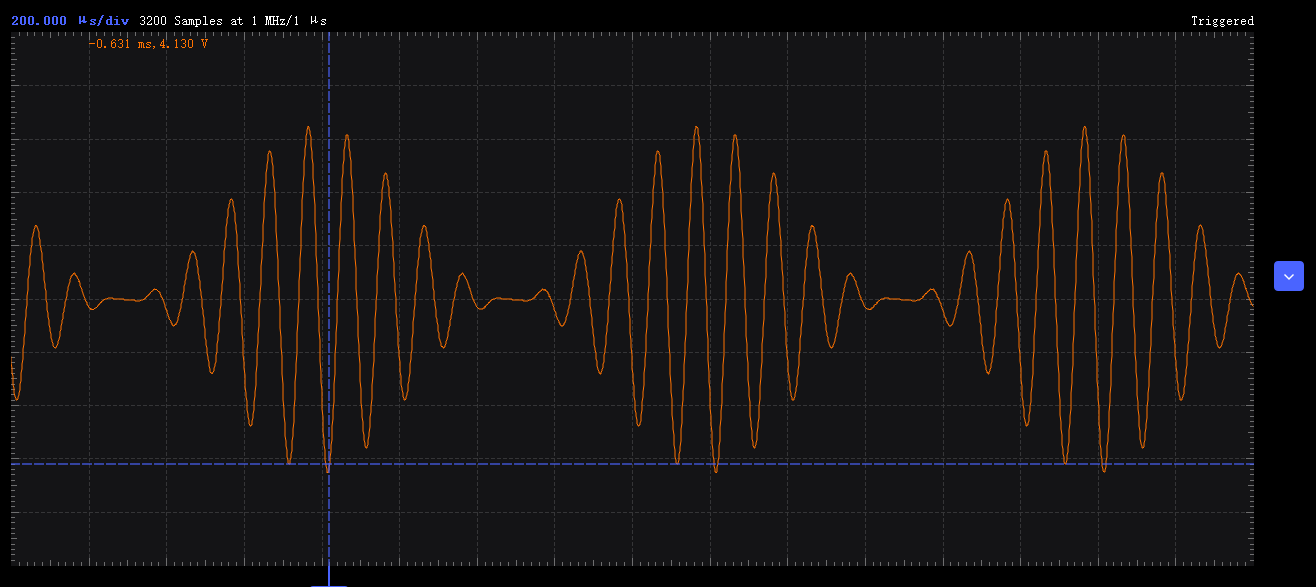

虚拟仪器ADALM2000在测试测量中的日常使用

第1节 - 电子系统设计流程及项目介绍

可编程信号发生器项目介绍、功能演示

硬件平台介绍、环境搭建

硬件平台

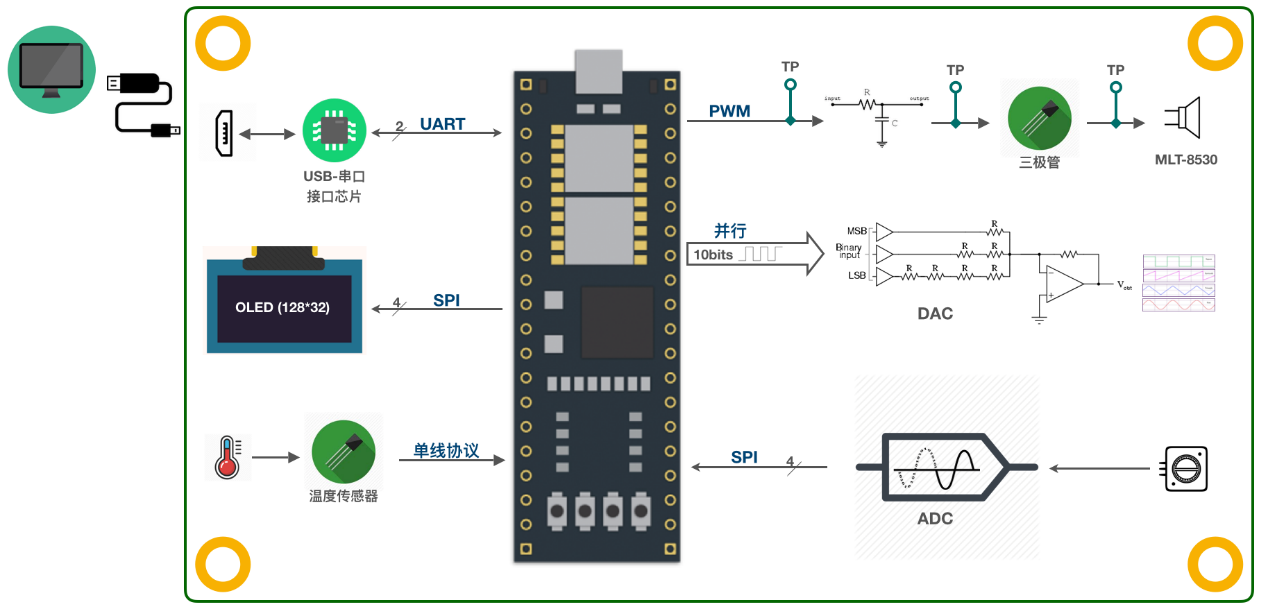

Training扩展板电路框图

开发环境

Lattice Diamond

百度云盘下载:https://pan.baidu.com/s/1W53MDQ1m60Lzz3oLJkKkFg 提取码:2k2v

Matlab

项目需求分析

项目方案对比、选择

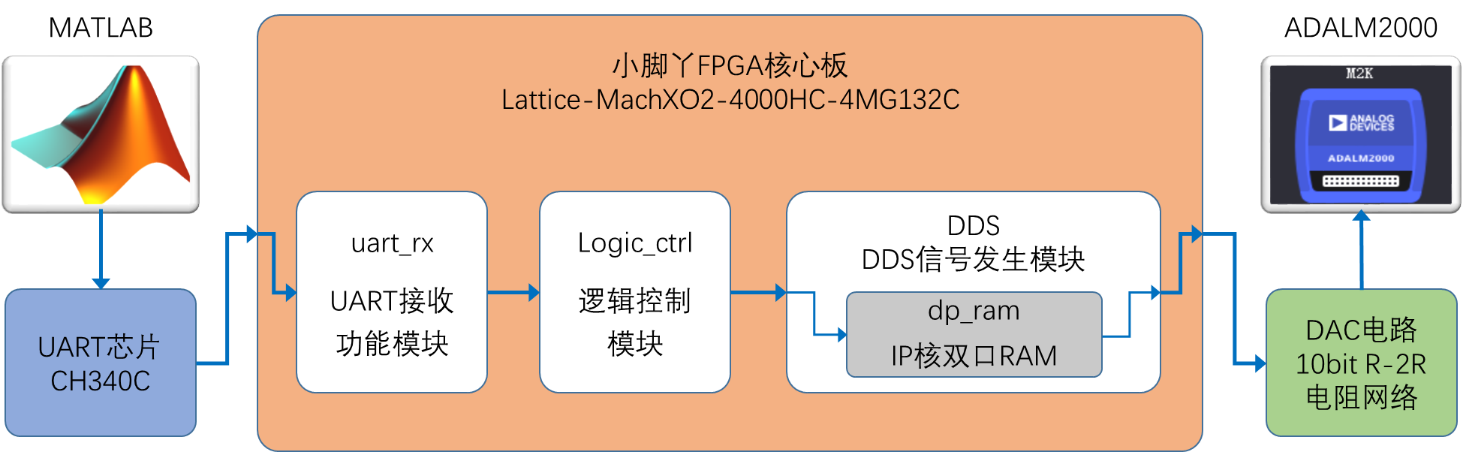

MATLAB+FPGA可编程信号发生器设计框架

第2节 - 认识FPGA

FPGA介绍

概念

架构

特点

LUT(Look Out Table)的逻辑电路实现

FPGA设计实现

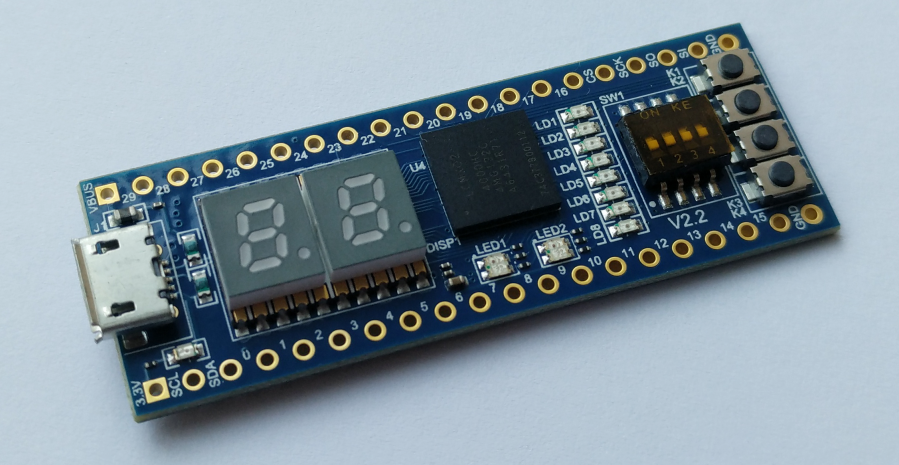

小脚丫FPGA核心板资料

图片

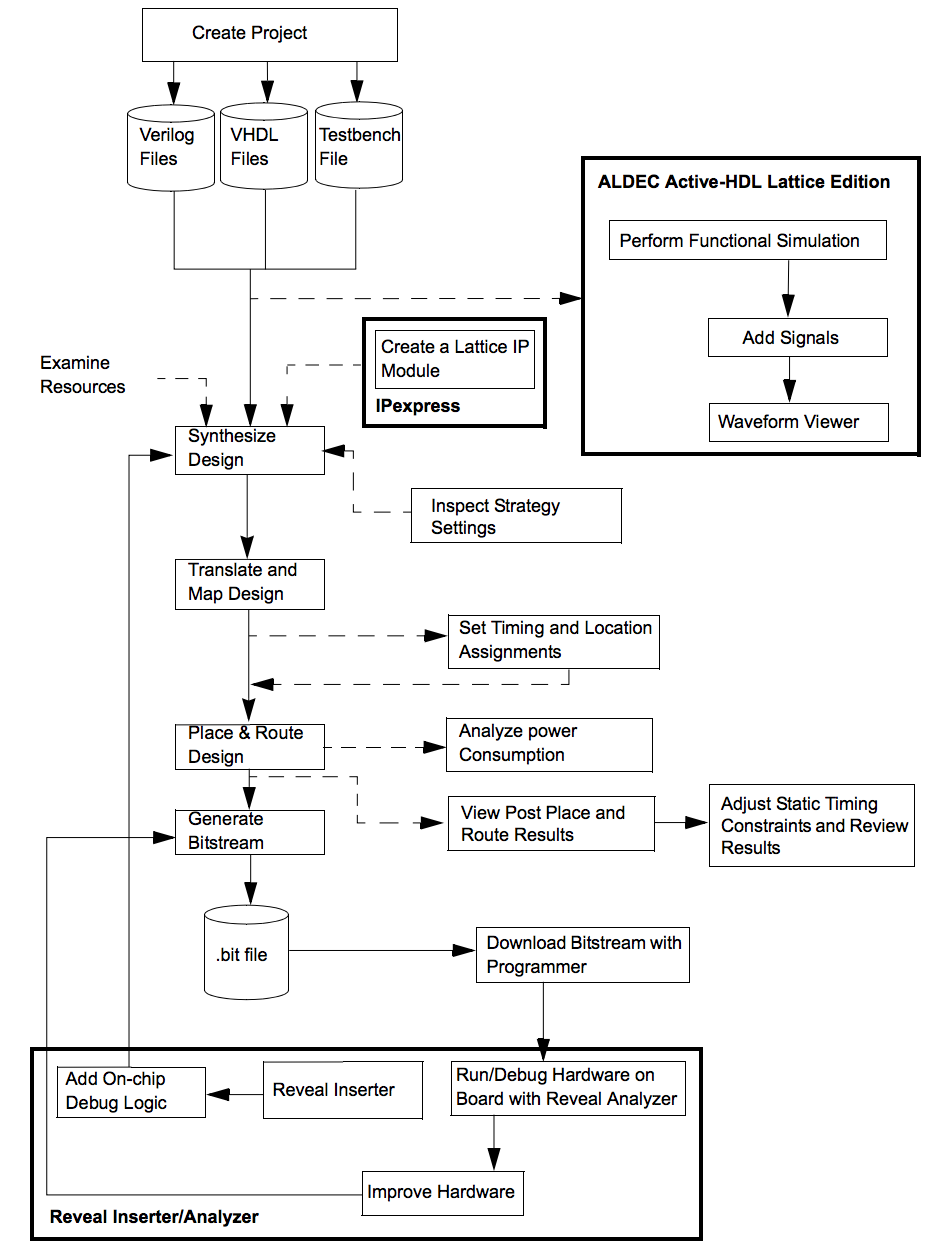

FPGA的设计流程演示

FPGA的仿真流程演示

FPGA学习资源推荐

第3节 - 组合逻辑及Verilog HDL学习

Verilog

HDL语言和语法介绍

基本变量类型

线网型变量

寄存器型变量

基本描述方式

数据流描述

行为级描述

实例化模型

基本赋值方式

阻塞赋值

非阻塞赋值

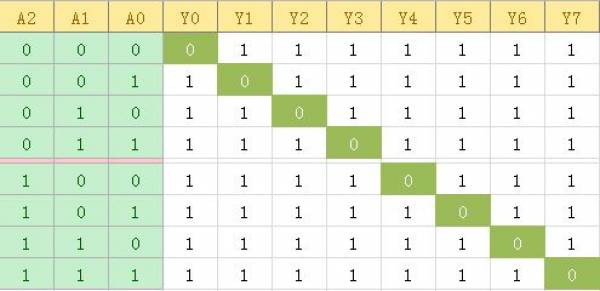

38译码器和数码管驱动设计

内部逻辑图

真值表

数据流描述实现

行为级描述实现

FPGA设计报告的理解

资源消耗

RTL Netlist

Floorplan View

Physical View

时序仿真理解组合逻辑

竞争

冒险

第4节 - 时序逻辑及Verilog HDL学习

Verilog

HDL语言和语法介绍

触发器和时序逻辑的理解

触发器的时序性

建立时间setup time

保持时间hold time

设计最大运行速率

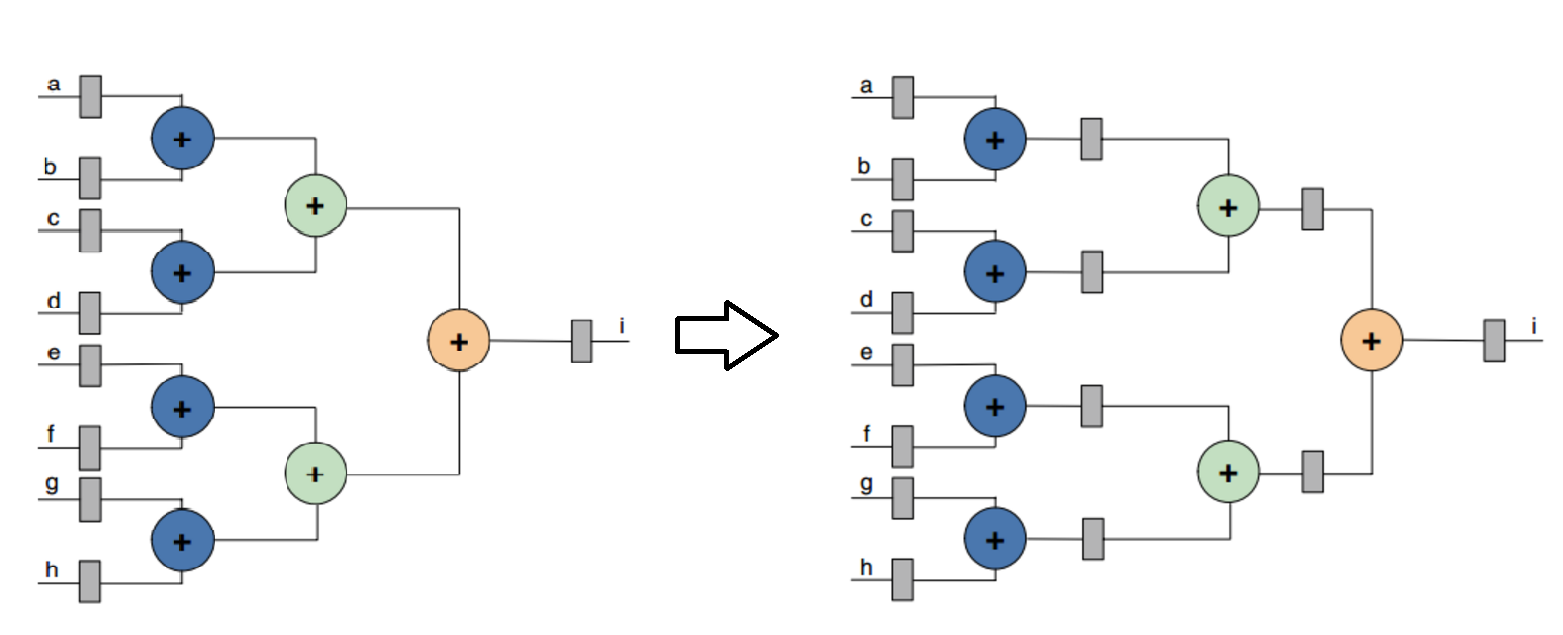

Pipeline“流水线”设计

计数器和流水灯设计实现

FPGA层次化设计和模块化设计

PWM脉宽调制的设计与应用

PWM调LED灯亮度

呼吸灯

PWM+RC电路实现DAC

第5节 - 有限状态机FSM设计学习

有限状态机

有限状态机的设计流程

交通灯设计实现

第6节 - IP核和Reveal在线分析工具使用

IP核例化

PLL核例化、仿真

RAM核例化

RAM初始化文件生成

Excel

matlab

波表生成器

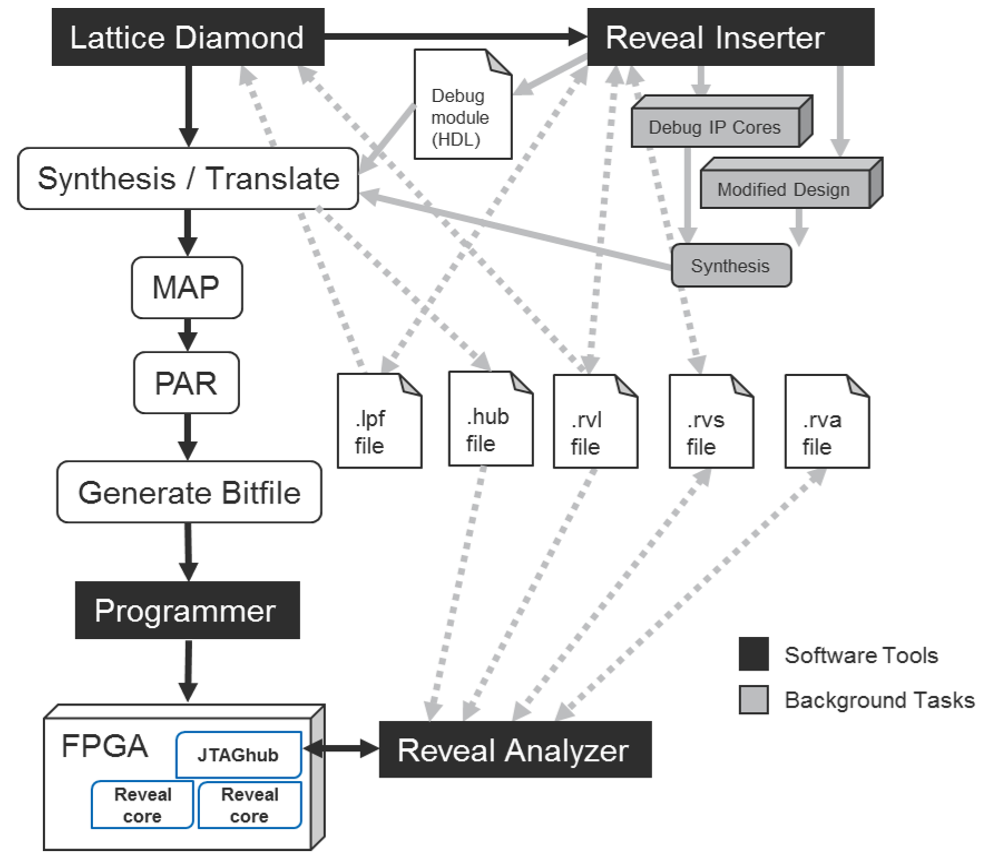

Reveal在线分析

工具介绍

Reveal

Inserter配置

Reveal Analyzer分析

第7节 - DDS原理与信号发生实现

R2R电阻网络DAC介绍

FPGA+R2R产生模拟输出

DDS原理介绍及调频调相功能实现

频率控制

相位控制

简易拨码信号发生器设计

第8节 - UART串口通信协议及实现

UART通信的特点和应用

ART通信协议和逻辑构成

UART通信接收功能的Verilog实现

UART通信数据传输验证

第9节 - Matlab串口功能实现

简易串口信号发生器设计

Matlab串口通信实现

查看Matlab串口通信的工作方式

Matlab+简易串口信号发生器控制实现

第10节 - 基于Matlab+FPGA的信号发生器设计

Matlab数据处理和UART数据发送方式确定

可编程信号发生器Logic_ctrl模块逻辑实现

8位简化可编程信号发生器实现

基于Matlab+FPGA的信号发生器设计实现及演示

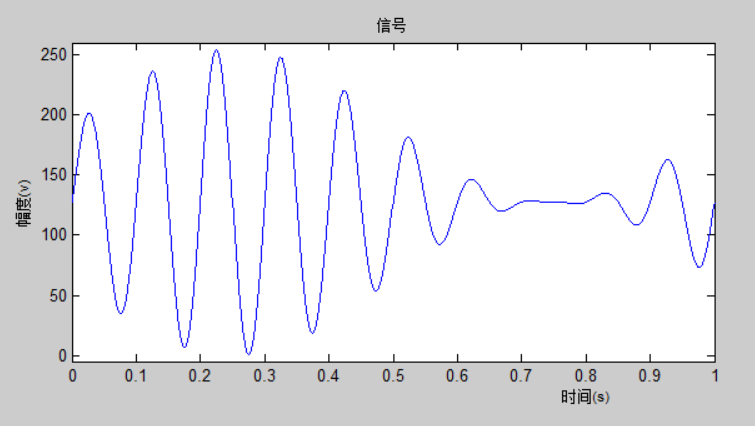

Matlab

信号发生

评论

0 / 100

查看更多

2020-02-29

4227

Copyright © 2024 苏州硬禾信息科技有限公司 All Rights Reserved 苏ICP备19040198号